近來全球重新認知半導體之戰略重要性,其中台灣的存在感更是不容忽視,最具代表性的就是全球頂級半導體代工廠如聯華電子(UMC)、台積電(TSMC),然而在幕後提供相關支援,使台灣相關企業能在半導體領域持續領跑的工業技術研究院(ITRI,以下簡稱ITRI)也功不可沒。ITRI已有50多年的歷史,是眾多新創企業的搖籃,並大力協助相關產業化過程。本次專訪ITRI電子與光電系統研究所張世杰所長,暢談一直以來ITRI在號稱全球最先進的台灣半導體產業領域扮演的角色,以及面對日新月異的半導體技術研究,包括最新趨勢之異質整合(heterogeneous integration)在內,ITRI又如何看待本身定位。

(受訪者簡歷)

工業技術研究院 電子與光電系統研究所所長

張世杰(Shih-Chieh Chang)

2022年就任ITRI電子與光電系統研究所所長,致力投入半導體、AI等新興技術開發,率領團隊描繪技術藍圖,啟動AI晶片關鍵技術研發,確立國家層級技術發展促進實證計畫之成功模式,對台灣半導體產業之自主研發影響匪淺。目前擔任台灣人工智慧晶片聯盟(AI on Chip Taiwan Alliance,AITA)副會長兼執行秘書。

| 台灣半導體產業與ITRI

一般之所以認為ITRI是台灣半導體產業的幕後推手,基於下列4大理由。首先, ITRI設有促進官民合作的相關部門。例如ITRI即與產業合作,成功推動磁阻式隨機存取記憶體(MRAM)※1相關研究,研發出之MRAM不僅速度之快傲視全球,效率也高。其次,ITRI並獲得國外資金援助,與國外大學合作進行MRAM相關研究,成功壓低耗電。

其次,ITRI也獲得政府資金挹注,同步推動先進半導體封裝技術相關研究,並在過程中累積了豐厚的技術、智財資產。ITRI不論在軟硬體領域均擁有眾多智慧財產,透過將相關knowhow回饋業界,致力提升台灣半導體業界之整體技術水準。

第三個理由為培育相關人才,也許過去相關人士較少提及這一點,但我個人認為相當重要。一直以來,透過在ITRI參與主要技術研究的工程師獨立創業,帶動技術回饋,刺激產業整體進一步活絡發展。相關業界經營者不少都是ITRI出身,相關專利總數超過30,000件,每年技術移轉件數也超過650件,獨立企業總計240家, ITRI OB研究人員更超過6,000人。

最後,則不得不提到眾多產學合作聯盟的存在。相關聯盟提供相關場域,讓產業界、學術界及研發機關三者得以積極合作,進行技術交流。除了橫向的技術交流外,還能促進縱向交流,例如系統廠商、零件廠商間合作。包括IC設計、Micro LED、顯示器相關的多個聯盟及化合物半導體聯盟在內,目前ITRI參與的聯盟至少超過10個,推動產學合作不遺餘力。其中當然也包括近來備受矚目的異質整合、小晶片封裝等相關聯盟,以及自駕車相關聯盟。作為台灣代表性研究機關,ITRI主動透過參與聯盟促進相關生態系建構,有助於加快半導體研發速度,並從中發掘眾多潛藏的技術種子,帶動技術進化。

| 備受矚目之半導體先進封裝開發課題與成果

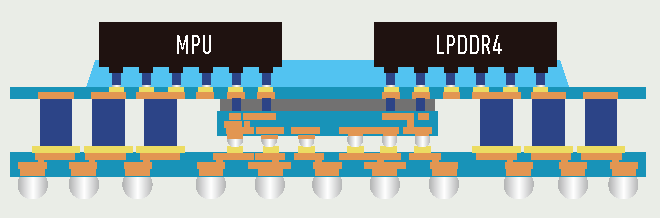

近年來,先進封裝技術日新月異, 2.5D、3D、扇出型(Fan-Out)封裝 等技術各位應該也是耳熟能詳。由於相關設計、流程複雜程度不可同日而語,以下想簡單介紹封裝工程師面對的相關課題及致力解決課題的相關研究成果。

首先,運用嶄新設計手法時必須符合高密度化、精密度提升要求,壓縮技術※2及成本課題也應運而生,包括TSV※3製造成本昂貴,以及初期不見得能確保高良率。其次還面對散熱課題,針對晶片積層封裝,如何散熱為重要課題。以下簡單介紹ITRI面對課題,如何推動相關研究並取得成果。

先進半導體封裝主要應用於多樣少量產品製造,相關市場要求的技術水準逐年提升,因應難度極高。

ITRI本身設有少量生產用2.5D、3D封裝試產產線,不少業界人士對試產產線十分感興趣,ITRI希望透過領先試產,致力支援業界推動產品量產化。

第二個成果則是小晶片相關開發。為了壓低耗電及追求性能提升,半導體代工業界持續推動製程改良,但成本卻也隨之節節攀升。尤其是半導體業界奉為圭臬的摩爾定律越接近3奈米

越面臨極限,製程微縮已不再是問題解決的萬靈丹,眾多業界人士期待小晶片有助於突破摩爾定律極限。

第三個成果的相關技術已經在市場上流通,前面也曾提到 矽中介層龐大且昂貴;相較之下,同樣作為2.5D封裝技術,英特爾的嵌入式多晶片互連橋接(Embedded Multi-die Interconnect Bridge,EMIB)技術不使用矽中介層,而是在封裝樹脂基板埋設名為「矽橋(silicon bridge)」的小型矽基板,得以壓低製造成本。雖然僅限無須高速訊號的產品使用,但因為使用低速互連而能壓低價格,帶動EMIB普及。很巧的,ITRI亦提出與英特爾EMIB概念接近的EIC(Embedded Interposer Carrier) 架構,但ITRI比英特爾更早取得專利(快2~3週)。與EMIB的不同處則在於EIC利用重新佈線(Redistribution layer,RDL)※4,配線能直達下方矽橋(EIC),無須重新設計晶片本身。

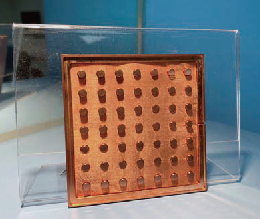

因應散熱課題的研究成果方面,想為各位介紹名為 TGP的薄型均溫板(金屬蓋)。小晶片採積層結構,難以散熱,因此思考如何散熱為重要課題。為了解決此一課題,ITRI開發了能貼在晶片上的TGP。TGP也採取多層結構,中間利用毛細管現象※5散熱。TGP中含水,晶片發熱導致水蒸發,向上移動散熱。水蒸氣冷卻後又變回水,循環使用。ITRI與台灣規模最大的散熱設備企業合作,目標為量產TGP。現階段TGP已經能進行超過200W的散熱,今後預計進一步改良,將對應散熱量提升到400W以上。以上謹針對ITRI在半導體領域的先進技術研究成果簡單介紹。

|

|

|

| 具專利架構的TGP Lid元件 | TGP Lid實際用於晶片上 |

| 伴隨電動車 (EV)普及乍然成為矚目焦點的功率半導體

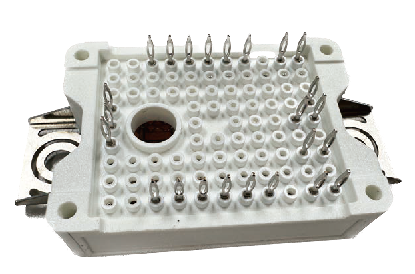

近年來伴隨EV普及,功率半導體成為矚目焦點,尤其功率模組封裝更是對應電動車需求的關鍵。

個人認為日本、歐洲在相關領域的技術十分先進,台灣也以黑馬之姿迎頭趕上。

功率元件及模組化重視散熱及可靠度議題,特別是功率元件高度發熱,必須採取相關對策,以免因過熱影響整體安全及性能。

ITRI在功率模組封裝投入相當多年的關鍵製程研究,包括晶片接合確保電性導通,材料與封裝結構匹配度的最佳化處理,以掌握良好的散熱效果及穩定性。

於晶片接合工程方面, ITRI曾與日本三井金屬共同研究銅燒結製程與材料,實證可將碳化矽晶片接合的孔隙率降到低於3%以下,此成果也持續導入於ITRI受託的功率模組試試製品項。

同時,累積的經驗已獲得不少車用關鍵組件業者青睞,委託終端應用開發案不在少數。

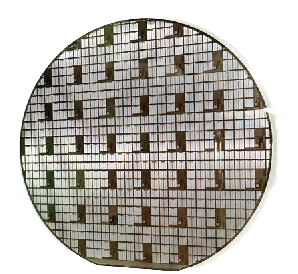

比如自主開發的高壓碳化矽元件並進而模組化工程後,整合於EV車用充電樁的實際案例,預定在今年(2023年)10月於名古屋電動車大展中公開。

|

|

|

| 工研院設計開發之碳化矽晶圓 | EV車用充電樁之碳化矽功率模組 |

| 對電子設計自動化(EDA)進化而言,提供廠商與設計人員的合作不可或缺

以上介紹的是過去ITRI之半導體業界相關對策及成果,最後想跟各位聊聊對相關研究而言不可或缺的電子設計自動化(EDA)。不論對半導體製造上游的IC設計公司或下游的代工業者而言,EDA都是非常重要的工具。首先,對上游而言,IC設計極度複雜,不使用EDA無法實現。

從設計、最適化、分析到模擬,都必須依賴EDA。越是複雜的設計,EDA的必要性就越高,也因此目前存在有眾多EDA,EDA本身也都十分複雜。例如編譯工具為了調整0到1間的眾多變量,必須控制數千個開關。各個開關的調整都必須具備深厚的EDA知識,要求設計人員完全掌握個別機能如何使用負擔沈重,也因此必須尋求廠商的應用工程師(AE)協助。此外,要是光靠AE的協助無法解決問題時,必須進一步借助工程師的力量。面對極度嚴苛的設計環境,必須具備眾多機能相關knowhow;然而為了對台灣國內面對相關課題的眾多中小企業提供協助,即使是大型EDA提供廠商也不見得擁有所有必要的資源。因此ITRI與大型EDA提供業者合作,在內部設置實驗室,致力支援台灣中小企業。

也許有點離題,但設計與工具的相關性其實十分重要。由於目前出現眾多嶄新設計手法, EDA提供業者為了將工具升級,必須理解相關設計手法。如果我沒記錯,2000年前後曾經出現一波電源門控(power gating)※6 風潮。但當時的EDA無法對應電源門控,設計公司開發門控相關技術時必須手動輸入。相關事實也恰巧證明了要是設備提供業者無法理解設計人員的作業型態,就無法開發EDA工具。

正如前述,設備提供業者如果想提升EDA的技術水準,必須針對糾錯(debug)尋求設計人員協助。據我所知,有幾家企業準備著手開發EDA,為了從多元角度出發糾錯,勢必需要尋求眾多用戶協助,過程應該十分嚴苛。設計人員的設計手法不一而足,但也正因為如此,必須由設計人員實際使用工具,嘗試錯誤,才能找出問題所在。

對代工業者而言,EDA也扮演重要角色。由於代工業者必須對設計人員提供流程設計套件(PDK)※7,EDA有助於將代工業者相關資訊轉換為設計人員需要的PDK。為了對設計人員提供最新流程資訊,必須具備代工業者先進製造技術的相關knowhow,才能考量PDK,設計出高良率的晶片。目前台積電正在推動2奈米、3奈米製程,過程中的微調需要取得眾多EDA相關協助。要是能獲得提供業者合作,可望加速流程微調,降低達成高良率的難度。ITRI與各家提供業者合作設置實驗室,今後也將透過此一實驗室,繼續扮演台灣半導體發展的幕後推手。

【註釋】

磁阻式隨機存取記憶體此一非揮發記憶體能高速讀寫,且積體程度、耐久性高,耗電量低,耐輻射等,長處眾多

後段製程之半導體封裝加工中,進行樹脂封裝時部分需要壓縮

高性能垂直互聯技術,透過單一晶片內的穿透孔,於多張積層晶片間傳送訊號、電源

指的是WLP之Fan-Out或2.5D實際封裝的設備結構中,以Cu與絕緣層形成之配線層。又名重新佈線層,串聯半導體晶片與外部取出部分

細管狀物體(毛細管)內側的液體未獲來自外部之能量,卻能在管中移動的物理現象

積體電路設計用技術,遮蔽未使用之電路區塊電流,以壓低耗電

特定半導體製程設計過程中之電路設計用資訊檔案群