概要

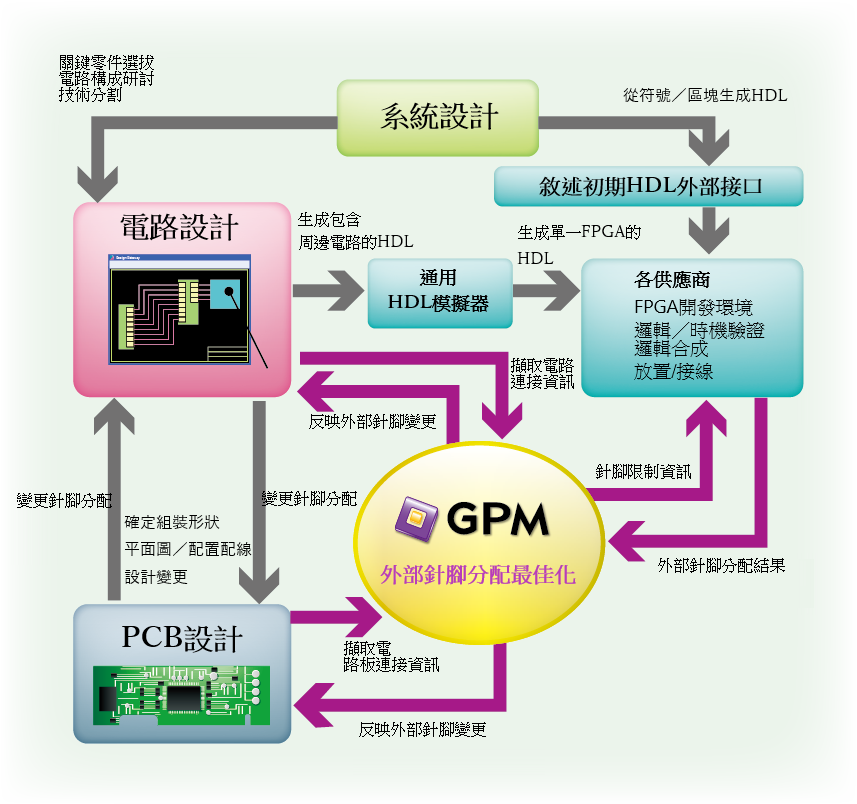

在要求高功能性、高集成化、低成本、短周期的背景下,FPGA元器件被廣泛用於各種領域。在詳細電路設計中,爲了提高速度或PCB板上的佈線效率等,電路設計、PCB板設計及FPGA設計的各設計流程必須進行磨合。

例如,根據PCB板佈局/層數的制約,需要研究及反映將FPGA元器件所連接的差動信號線或總線等分配給那個引脚。這種磨合工作的頻率高、信息量大,會對各設計流程造成負擔,也是引發人爲錯誤的主要原因。

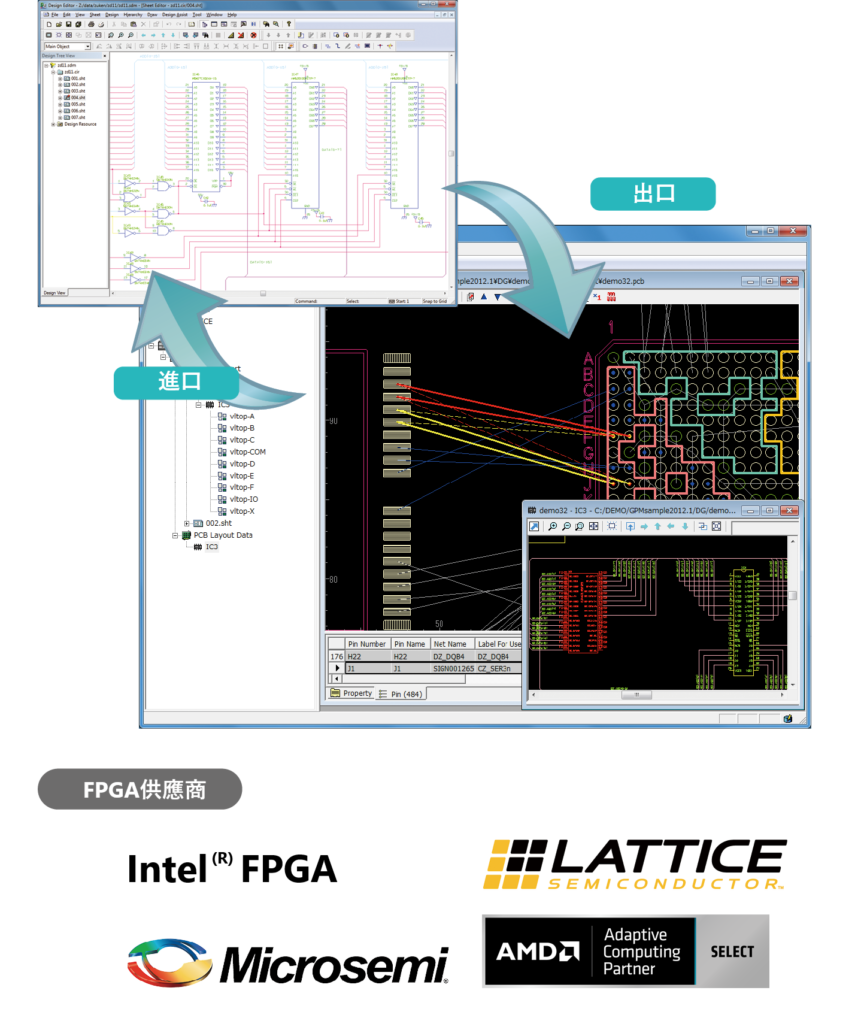

GPM在各設計流程的基礎上,還追求包括了CAD庫管理在內的協同作業,使圍繞FPGA元器件的電路/PCB板設計整體實現最優化。

●CAD庫、FPGA、電路、PCB板這4個流程的協同作業

●使圍繞FPGA元器件的PCB板設計整體實現最優化

●圖形化的視圖使信息可視化

●提供直觀的工具操作環境